# **Short-Form Specification**

The STD 32 Bus Specification

# STD32

# 🛛 🖕 🗛 Brief\_Overview

The *STD 32 Bus Specification* extends the capabilities of the STD-80 Series standard, while remaining compatible with existing STD Bus cards. These excerpts from the specification provide mechanical and electrical details pertinent to a technical evaluation of the bus. For the complete specification, contact the STD 32 Manufacturers Group.

## Mechanical

## Connectors

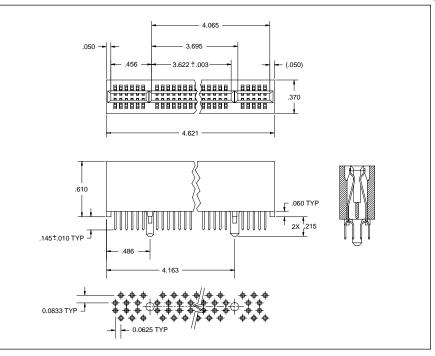

The 136-pin STD 32 card connector uses cantilever beam construction with a hemispherical contact point. This connector/contact style is similar to PC and Micro Channel designs, and is considered one of the most reliable in the industry (see **Figure 1**).

## **Connector Specifications**

- Number of Contacts: 136

- Contact Design: Cantilever beam, hemispherical contact point

- Contact Plating: 30 microinches of gold over 50 microinches nickel (minimum)

- *Current Capacity:* 1.0 Amp (minimum per pin)

- *Mating PCB Thickness:* 0.062 inch ±0.007 inch

- Operating Temperature: -40° to +85° C

- Mating Cycles: 500 (minimum)

**Figure 1.** The STD 32 connector contacts are arranged as 68 directly opposed pairs. The center section of 57 contact pairs provide backward compatibility with older STD-style cards and expansion to 16-bit non-multiplexed transfers. The remaining 11 contact pairs on the card extensions allow 32-bit non-multiplexed data transfers while maintaining compatibility with older 8-bit STD I/O cards.

- Insertion Force:

- 6 ounces per contact pair

- *Vibration:* 10 Hz to 2 KHz at 15 Gs with 0.06-inch displacement

- Contact Normal Force: 135 grams per contact

- Connector Body: Glass-filled polyphenylene sulfide, UL 94V-0

- Insulation Resistance: Greater than 50,000 Megohms

- Operating Humidity: 0 to 95% with no condensation

## **Connector Mating Surfaces**

The design of the connector mating surface (or "gold fingers") is the core of the *STD 32 Bus Specification*. This design not only allows the number of contacts to increase from 56 to 136 but also provides a backward-compatible platform for the thousands of older STD I/O cards currently available for the STD Bus.

## **Mating Surface Specifications**

- PCB Thickness:

- 0.062 Inch ±0.007 inch

- Plating:

30 microinches of gold over 50 microinches of nickel

• Design:

Conforms to STD 32 P/E finger dimensions

## Backplane

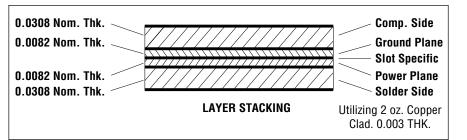

Another critical component in an STD 32 system is the backplane. The backplane design incorporates several important features including increased backplane signal impedance. A higher backplane signal impedance means "cleaner" signals are sent across the backplane. That is, ringing and reflections are minimized. This is especially important during signal transitions between the TTL threshold regions of 0.8v and 2.0v (see **Figure 2**).

#### **Backplane Specifications**

- *Minimum Center-to-Center Trace Spacing: 16 mil*

- Minimum Trace Width: 8 mil

- *Number of Copper Planes:* 5 maximum

- Unloaded Impedance: 55 ohms (minimum)

- Copper Clad Thickness: 2 oz.

- Backplane PCB Thickness: 0.093-inch (minimum)

## Electrical

#### **Pin Descriptions**

# See Figures 3 and 4.

# **Clock Frequency**

The STD 32 Bus uses the signal CLOCK\* for synchronous communication between Bus Masters (CPUs) and peripheral boards, and for other system management features such as arbitration. The Permanent Master is responsible for driving CLOCK\* in all systems. The CLOCK\* frequency is 8 MHz.

## **Transfer Types**

STD 32 defines five classes of backplane transfers for communication between Bus Masters and peripherals. Standard Architecture (SA) transfers define compatible cycles for older STD-80 Series peripherals. Both 8and 16-bit SA transfers are allowed through dynamic bus sizing. Extended Architecture (EA) transfers support 8-, 16-, and 32-bit data widths with a transfer cycle as short as one CLOCK\* cycle. The maximum bandwidth for EA transfers is 32 Mbytes/ second (see Figure 5). The cycle performed is dynamically sensed by the Bus Master from control signals that the peripheral returns. The default cycle is an SA 8-bit (SA8) cycle

to remain compatible with older technology cards designed around the STD-80 Series specification.

#### **Address Space**

STD 32 supports a full 32-bit address space for memory cycles and a full 16-bit address space for I/O cycles. Older boards that do not decode the full I/O address range are allowed if they decode the IOEXP signal. IOEXP is driven low by STD 32 CPU boards in the I/O range FC00h to FFFFh, and high for all other addresses.

This mechanism prevents I/O boards that decode less than 16 bits and IOEXP low from being redundantly mapped throughout the I/O space. All STD 32 I/O boards must decode the full 16-bit address space. STD 32 memory boards must decode 24 bits of address for SA cycles and 32 bits of address for EA cycles.

## Standard Architecture (SA) Cycles

SA cycles are nominally five CLOCK\* cycles. The upper 8 bits of memory address (A16 to A23) is mul-

tiplexed with the data lines to allow the full, 16 Mbyte address range required by 286 and 386SX processors. This multiplexing scheme is compatible with STD-80 Series boards. 8-bit data transfers are performed unless the memory board being accessed returns MEM16\* at the beginning of the cycle. When MEM16\* is returned, a 16-bit SA cycle is defined (SA16), and the additional data signals D8 to D15 are driven on non-multiplexed pins. I/O cycles can also be 16 bits if the signal IO16\* is driven by the I/O board during the transfer.

## Extended Architecture (EA) Cycles

STD 32's default transfer is an SA class cycle. If, during the beginning of a cycle, EX8\*, EX16\*, or EX32\* is driven low by a peripheral board, then Extended Architecture cycles are performed. EX8\*, EX16\*, and EX32\* define 8-, 16-, and 32-bit EA transfer capability, respectively. Burst cycles are also possible for EA devices when the peripheral drives

| COMPONENT SIDE                                                                                                                                                                     |                                                                                                                                                                                                                                      |                                                                                                                                    | CIRCUIT SIDE                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                         |                                                                                                                                                                                                                                                             |                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin                                                                                                                                                                                | Mnemonic                                                                                                                                                                                                                             | Signal Flow                                                                                                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Pin                                                                                                                                                                                     | Mnemonic                                                                                                                                                                                                                                                    | Signal Flow                                                                                                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1<br>3<br>5<br>7<br>9<br>11<br>13<br>15<br>7<br>9<br>11<br>13<br>25<br>27<br>29<br>31<br>33<br>5<br>7<br>29<br>31<br>33<br>5<br>37<br>39<br>41<br>43<br>45<br>47<br>49<br>51<br>55 | +5VDC<br>GND<br>VBAT<br>A19/D3<br>A18/D2<br>A17/D1<br>A16/D0<br>A7<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>A0<br>WR*<br>IORQ*<br>IOEXP<br>INTR01*<br>STATUS1*<br>BUSAK*<br>INTR01*<br>SYSRESET*<br>CLOCK*<br>PCO<br>AUX GND<br>AUX +V | In<br>Bidir<br>Out/Bidir<br>Out/Bidr<br>Out/Bidr<br>Out/Bidr<br>Out<br>Out<br>Out<br>Out<br>Out<br>Out<br>Out<br>Out<br>Out<br>Out | Logic Power<br>Logic Ground<br>Battery Power<br>Address/Data<br>Address/Data<br>Address/Data<br>Address/Data<br>Address<br>Address<br>Address<br>Address<br>Address<br>Address<br>Address<br>Address<br>Address<br>Address<br>Address<br>Write Mem or I/O<br>I/O Address Select<br>I/O Expansion<br>Interrupt Request 1<br>CPU Status 1<br>Bus Acknowledge<br>Wait Request<br>System Request<br>Clock<br>Priority Chain Out<br>AUX Ground (bussed)<br>AUX Positive (+12VDC) | $\begin{array}{c} 2\\ 4\\ 6\\ 8\\ 10\\ 12\\ 14\\ 16\\ 18\\ 20\\ 22\\ 24\\ 28\\ 30\\ 22\\ 24\\ 30\\ 33\\ 40\\ 44\\ 46\\ 8\\ 50\\ 25\\ 5\\ 5\\ 5\\ 5\\ 5\\ 5\\ 5\\ 5\\ 5\\ 5\\ 5\\ 5\\ 5$ | +5VDC<br>GND<br>DCPDN*<br>A23/D7<br>A22/D6<br>A21/D5<br>A14<br>A13<br>A12<br>A13<br>A12<br>A11<br>A13<br>A12<br>A11<br>A10<br>A9<br>A8<br>RD*<br>MEMRQ*<br>BHE*<br>STATUSO*<br>BUSRQ*<br>INTRQ*<br>NMIRQ*<br>PBRESET*<br>CNTRL*<br>PCI<br>AUX GND<br>AUX -V | In<br>In<br>Bidir<br>Out/Bidir<br>Out/Bidr<br>Out/Bidr<br>Out/<br>Out<br>Out<br>Out<br>Out<br>Out<br>Out<br>Out<br>Out<br>Out<br>Out | Logic Power<br>Logic Ground<br>DC Power Down<br>Address/Data<br>Address/Data<br>Address/Data<br>Address/Data<br>Address<br>Address<br>Address<br>Address<br>Address<br>Address<br>Address<br>Address<br>Address<br>Address<br>Address<br>Address<br>Address<br>Address<br>Address<br>Address<br>Address<br>Address<br>Address<br>Address<br>Address<br>Address<br>Address<br>Address<br>Address<br>Byte High Enable<br>CPU Status 0<br>Bus Request<br>Interrupt Request<br>Non-Maskable Int Req |

Notes: An asterisk (\*) indicates a low level active signal. Address lines A16 to A23 are multiplexed on data lines D0 to D7 on each address cycle for STD-80 compatibility. PCO and PCI are not typically used on peripheral cards. All boards not supporting PCO and PCI should tie these two signals together.

*Figure 3.* This table illustrates the STD 32 Bus P Pinouts (Table 3-2 in the STD 32 specification). See the next page for a description of the E Pinouts.

SLBURST\*, while the Bus Master is driving MSBURST\*. Burst cycles allow up to 32 bits of data to be transferred on every CLOCK\*, for a 32 Mbyte/second transfer rate. The nominal cycle (non-burst) is a two-CLOCK\* cycle. EA cycles use separate data and address signals (not multiplexed) to allow pipelined execution of the transfer.

#### **Direct Memory Access (DMA)**

Backplane Direct Memory Access (DMA) transfers are also defined for the Extended Architecture, at up to 32 Mbytes/second. Each of the first 15 slots in an STD 32 card cage has a dedicated set of DMA control signals to allow for true backplane DMA transfers. Older technology DMA mechanisms on the STD bus have required front plane cabling.

## Interrupt Topology

STD 32 defines five bused inter-

|                                                                                                                                         | CO                                                                                                                                                                                                                                     | MPONENT                                                                                                                                                                                                                                                    | SIDE                                                                                                          |                                                                                                                                                                                                                   | (                                                                                                                                                                                                                           | CIRCUIT SI                                                                                                                                                                                         | DE                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Pin                                                                                                                                     | Mnemonic                                                                                                                                                                                                                               | Signal Flow                                                                                                                                                                                                                                                | Description                                                                                                   | Pin                                                                                                                                                                                                               | Mnemonic                                                                                                                                                                                                                    | Signal Flow                                                                                                                                                                                        | Descrip                                                                                    |

| 1<br>3<br>5<br>7<br>9<br>11                                                                                                             | +5 VDC<br>XA19<br>XA18<br>XA17<br>XA16<br>NOWS*                                                                                                                                                                                        | In<br>Out<br>Out<br>Out<br>In                                                                                                                                                                                                                              | Logic Ground<br>Address<br>Address<br>Address<br>Address<br>No Wait States                                    | 2<br>4<br>6<br>8<br>10<br>12                                                                                                                                                                                      | LOCK*<br>XA23<br>XA22<br>XA21<br>XA20<br>RSVD                                                                                                                                                                               | Out<br>Out<br>Out<br>Out<br>Out                                                                                                                                                                    | Lock<br>Addres<br>Addres<br>Addres<br>Addres<br>Reserv                                     |

| $\begin{array}{c} 13\\ 15\\ 17\\ 19\\ 22\\ 27\\ 29\\ 31\\ 33\\ 35\\ 37\\ 39\\ 41\\ 43\\ 55\\ 55\\ 55\\ 61\\ 63\\ 65\\ 69\\ \end{array}$ | +5VDC<br>DAKx*<br>GND<br>D26<br>D27<br>D26<br>D25<br>D24<br>D23<br>D22<br>D21<br>D20<br>GND<br>D19<br>D18<br>B017<br>D16<br>GND<br>D17<br>D16<br>GND<br>BE1*<br>BE0*<br>MEM16*<br>M-I0<br>DMAIOW*<br>I016*<br>CMD*<br>EXRDY<br>INTRQ3* | In<br>Out<br>In<br>Bidir<br>Bidir<br>Bidir<br>Bidir<br>Bidir<br>Bidir<br>Bidir<br>Bidir<br>Bidir<br>Bidir<br>In<br>Out<br>Out<br>Out<br>Out<br>Out<br>In<br>In<br>Out<br>Out<br>In<br>In<br>Out<br>Out<br>In<br>In<br>Out<br>Out<br>In<br>In<br>Out<br>Out | Logic Power<br>DMA Acknowledge<br>Logic Ground<br>Data<br>Data<br>Data<br>Data<br>Data<br>Data<br>Data<br>Dat | 14<br>16<br>18<br>20<br>22<br>4<br>26<br>28<br>30<br>32<br>33<br>34<br>36<br>38<br>34<br>36<br>38<br>34<br>42<br>44<br>46<br>48<br>50<br>52<br>54<br>55<br>52<br>54<br>56<br>8<br>60<br>62<br>64<br>66<br>8<br>70 | +5VDC<br>DREQx*<br>GND<br>D30<br>D30<br>D29<br>D28<br>GND<br>D15<br>D14<br>D13<br>D12<br>D11<br>D10<br>D9<br>D8<br>MASTER16*<br>AENx*<br>BE3*<br>GND<br>W-R<br>DMAIOR*<br>EX8*<br>START*<br>EX32*<br>T-C<br>+5VDC*<br>MREQx | In<br>In<br>Bidir<br>Bidir<br>Bidir<br>Bidir<br>Bidir<br>Bidir<br>Bidir<br>Bidir<br>Bidir<br>Bidir<br>Bidir<br>Bidir<br>Out<br>Out<br>Out<br>Out<br>Out<br>Out<br>In<br>Bidir<br>In<br>Bidir<br>In | Logic F<br>DMA R<br>Logic G<br>Data<br>Data<br>Data<br>Data<br>Data<br>Data<br>Data<br>Dat |

| 71<br>73<br>75<br>77<br>79                                                                                                              | SLBURST*<br>XA27*<br>XA26*<br>XA25*<br>XA24*                                                                                                                                                                                           | In<br>Out<br>Out<br>Out<br>Out                                                                                                                                                                                                                             | Slave Burst<br>Address<br>Address<br>Address<br>Address<br>Address                                            | 72<br>74<br>76<br>78<br>80                                                                                                                                                                                        | MSBURST*<br>XA31*<br>XA30*<br>XA29*<br>XA28*                                                                                                                                                                                | Out<br>Out<br>Out<br>Out<br>Out                                                                                                                                                                    | Master<br>Addres<br>Addres<br>Addres<br>Addres                                             |

Figure 4. This table illustrates STD 32 Bus E Pinouts.

rupt signals and one slot-specific interrupt for application use and system management.

#### **Bused Interrupts**

INTRO\*, INTRO1\*, INTRQ2\*, INTRQ3\*, and NMIRQ\* are bused signals between all STD 32 connectors, including Slot

transfer types X. Bus Masters use these signals for interrupt signaling between peripherals or Bus Masters and other Bus Masters.

#### **Slot-Specific Interrupts**

Each of the first 15 slots of the STD 32 card cage has a dedicated interrupt between it and the Slot X connector (the last connector on the left side of the backplane). For Bus Masters that can interface to Slot X,

|          | CIRCUIT SIDE    |                |                               |  |  |  |

|----------|-----------------|----------------|-------------------------------|--|--|--|

|          |                 |                | (                             |  |  |  |

| Pin      | Mnemonic        | Signal Flow    | Description                   |  |  |  |

| 2        | LOCK*           | Out            | Lock                          |  |  |  |

| 4        | XA23<br>XA22    | Out            | Address                       |  |  |  |

| 8        | XA22<br>XA21    | Out<br>Out     | Address<br>Address            |  |  |  |

| 10       | XA20            | Out            | Address                       |  |  |  |

| 12       | RSVD            |                | Reserved                      |  |  |  |

| 14       | +5VDC           | In             | Logic Power                   |  |  |  |

| 16<br>18 | DREQx*<br>GND   | In             | DMA Request                   |  |  |  |

| 20       | D31             | ln<br>Bidir    | Logic Ground<br>Data          |  |  |  |

| 22       | D30             | Bidir          | Data                          |  |  |  |

| 24       | D29             | Bidir          | Data                          |  |  |  |

| 26       | D28             | Bidir          | Data                          |  |  |  |

| 28       | GND             | In             | Logic Ground                  |  |  |  |

| 30<br>32 | D15<br>D14      | Bidir<br>Bidir | Data<br>Data                  |  |  |  |

| 34       | D14             | Bidir          | Data                          |  |  |  |

| 36       | D12             | Bidir          | Data                          |  |  |  |

| 38       | D11             | Bidir          | Data                          |  |  |  |

| 40       | D10             | Bidir          | Data                          |  |  |  |

| 42       | D9<br>D8        | Bidir          | Data                          |  |  |  |

| 44       | MASTER16*       | Bidir<br>Out   | Data<br>Master 16-bit         |  |  |  |

| 48       | AENx*           | Out            | Address Enable                |  |  |  |

| 50       | BE3*            | Out            | Byte Enable 3                 |  |  |  |

| 52       | BE2*            | Out            | Byte Enable 2                 |  |  |  |

| 54       | GND             | In             | Logic Ground                  |  |  |  |

| 56<br>58 | W-R<br>DMAIOR*  | Out<br>Out     | Write or Read<br>DMA I/O Read |  |  |  |

| 60       | EX8*            | In             | Exchange 8-bit                |  |  |  |

| 62       | START*          | Out            | Start                         |  |  |  |

| 64       | EX32*           | In             | Exchange 32-bit               |  |  |  |

| 66       | T-C             | Bidir          | Terminate or Count            |  |  |  |

| 68<br>70 | +5VDC*<br>MREQx | In<br>In       | Logic Power<br>Master Request |  |  |  |

| 72       | MSBURST*        | Out            | Master Burst                  |  |  |  |

| 74       | XA31*           | Out            | Address                       |  |  |  |

| 76       | XA30*           | Out            | Address                       |  |  |  |

| 78       | XA29*           | Out            | Address                       |  |  |  |

| 80       | XA28*           | Out            | Address                       |  |  |  |

| Transfer | Nominal          | Burst Transfer   |  |  |

|----------|------------------|------------------|--|--|

| CLASS    | Transfer Rate    | Rate             |  |  |

| SA8      | 2 Mbytes/second  | N/A              |  |  |

| SA16     | 4 Mbytes/second  | N/A              |  |  |

| EA8      | 4 Mbytes/second  | N/A              |  |  |

| EA16     | 8 Mbytes/second  | 16 Mbytes/second |  |  |

| EA32     | 16 Mbytes/second | 32 Mbytes/second |  |  |

Figure 5. Theoretical bandwidths for STD 32

this allows up to 15 interrupt sources in addition to the five bused interrupts.

#### **Multiprocessor Arbitration**

The Slot X connector on STD 32 backplanes allows for a centralized arbitration scheme for up to 15 Bus Masters. Each slot has dedicated arbitration signals (MREQx\*/MAKx\*) which are used to gain control of the bus. EA Temporary Masters use the MREQx\*/MAKx\* signals for bus arbitration. SA Temporary Masters use a similar approach, but use the DREQx\*/DAKx\* signals for bus ownership. A centralized arbiter manages bus ownership between Temporary Masters and the Permanent Master. Rotating priority or optional fixed priority can be selected.

#### **Compliance Levels**

Compliance levels specify the capabilities of STD 32 board designs. Each bus-related feature, such as the ability to support EA or SA transfers, is given a mnemonic description to be used on data sheets and board specifications to assist customers in system configuration.

#### **Board MODES**

There are five board MODES within STD 32 as defined in Figure 6. MODES define how a board may be used. For instance, a CPU board would normally be a Permanent Master but when another Bus Master has control it might also support memory cycles to or from it by the Temporary Master. In this case the board would have two board MODES, Permanent Master and Memory Slave.

| STD 32 Board MODE | Definition                                                                                       |  |  |

|-------------------|--------------------------------------------------------------------------------------------------|--|--|

| Permanent Master  | Bus master that drives CLOCK*, monitors PBRESET*, and drives SYSRESET*                           |  |  |

| Temporary Master  | Bus Master that requests the bus via BUSRQ*, MREQx, or DREQx*                                    |  |  |

| I/O Slave         | Slave that decodes and responds to SA or EA I/O cycles                                           |  |  |

| Memory Slave      | Slave that decodes and responds to SA or EA memory cycles                                        |  |  |

| Arbiter (Mn,Dn)   | System arbiter that manages n MREQx*/MAKx* signals and/or n DREQx*/DAKx* signals for arbitration |  |  |

Figure 6. STD 32 compliance board MODES

#### **Compliance CLASSES**

For each board MODE, there are several CLASSES of transfers sup-

ported for that CLASS. Standard Architecture (SA) 8-bit and 16-bit transfer CLASSES are defined as SA8 and

| Feature    | Description                                                                                                                         | Additional Signal Support                               |

|------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| A16        | SA 16-bit I/O address decode (I/O Slave)/ generation (master)                                                                       | A0-A15                                                  |

| A10<br>A24 | SA 10-bit i/O address decode (i/O Slave)/ generation (master)<br>SA 24-bit memory address decode (Memory Slave)/generation (master) | A0-A15<br>A0-A24                                        |

| D8         | SA 8-bit data transfer, masters/slaves                                                                                              | D0-D7                                                   |

| D16        | SA 16-bit transfer, masters/slaves                                                                                                  | D0-D15,MEM16*,BHE*,I016*                                |

| EBURST     | EA Burst transfer capability, masters/slaves                                                                                        | SLBURST*,MSBURST*                                       |

| EDMAA      | EA buist transfer capability, masters/slaves                                                                                        | DMAIOW*,DMAIOR*, DRQx,DAKx*,T-C                         |

| EDMAR      |                                                                                                                                     |                                                         |

|            | EA type B DMA transfers supported, masters/slaves                                                                                   | DMAIOW*, DMAIOR*, DRQx, DAKx*, T-C                      |

| EDMAC      | EA type C DMA transfers supported, masters/slaves                                                                                   | DMAIOW*,DMAIOR*, DRQx, DAKx*,T-C,<br>SLBURST*, MSBURST* |

| GAX        | EA geographical address support masters/slaves                                                                                      | AENx* (masters)                                         |

| I          | SA (STD-80) interrupt generation (slaves)/ servicing (masters) on INTRQ*, INTR1*,NMIRQ*, CNTRL* (INTRQ2*), or INTRQ3*               | INTRQ*,INTRQ1*,NMIRQ*<br>[CNTRL* (INTRQ2*)], INTRQ3*    |

| ICA        | Cascadable interrupt address support, masters/slaves                                                                                | A8-A10 during INTA                                      |

| IXP        | Slot-specific interrupt servicing (Permanent Masters)/<br>generation (slaves), positive edge-triggered                              | IRQx                                                    |

| IXL        | Slot-specific interrupt servicing (Permanent Masters)/<br>generation (slaves), low-level asserted                                   | IRQx                                                    |

| MB         | Bus arbitration via BUSRQ*/BUSAK* - SA Masters only                                                                                 | BUSRQ*,BUSAK*                                           |

| MD         | Bus Arbitration via DREQx*/DAKx* - SA Masters only                                                                                  | DREQx*, DAKx*                                           |

| МХ         | Bus Arbitration via MREQx*/MAKx* (Permanent Master)/<br>request (Temporary Slave)                                                   | MREQx*,MAKx*                                            |

| NOWS       | No wait-state (NOWS*) support                                                                                                       | NOWS*                                                   |

| SDMA8      | 8-bit SA frontplane DMA as specified in Chapter 2,<br>masters/slaves                                                                |                                                         |

| SDMA16     | 16-bit SA frontplane DMA as specified in Chapter 2, masters/slaves                                                                  |                                                         |

| XA16       | EA 16-bit address decode, I/O transfers                                                                                             | A2-A15, BE0*-BE3* as per Chapter 3                      |

| XA32       | Full 32-bit EA address space driven, masters may pull XA24*-XA31*<br>passively high Full 32-bit EA address decoded by Memory Slaves | A2-A15, XA16-XA23, XA24* XA31*,<br>BE0*-BE3*            |

| XD8        | 8-bit EA data transfer, masters/slaves                                                                                              | D0-D7                                                   |

| XD16       | 16-bit EA data transfer, masters/slaves                                                                                             | D0-D15, EX16*, BE0*-BE3*                                |

| XD32       | 32-bit EA data transfer, masters/slaves                                                                                             | D0-D31, EX16*, EX32*, EX32* BE0* BE3*                   |

Figure 7. STD 32 compliance product descriptor feature listing

SA16 respectively. Extended Architecture (EA) 8-, 16-, and 32-bit transfer CLASSES are defined as EA8, EA16, and EA32, respectively.

## *Compliance Product Description* Features (Requirements/ Options)

Listed after the CLASS support for each board MODE is a string of required and/or optional features that the board supports. Requirements are items such as interrupt support or DMA that a board needs in order to operate. Options are items that may be used by a board but are not required for operation. Possible features for STD 32 compliance codes are found in **Figure 7**.

## **Compliance Style**

Technical data sheets for STD 32compatible boards include a product descriptor. This shows that the board complies with the STD 32 specification in all board MODES, transfer CLASSES, and required or optional features listed (see **Figure 8**).

For example, a board that can be either a Permanent Master or a Temporary Master with full EA8, EA16, EA32, SA8, and SA16 transfer CLASS support, interrupt support, cascade interrupt control, and that supports SA8 memory transfers to or from it when it is not in control, would have the following product descriptor: STD 32 Compliance Permanent Master: EA32, EA16, EA8, SA16, SA8 - MX, MB, ICA, I Temporary Master: EA32, EA16, EA8, SA16, SA8 - {MX}, MB, ICA, I Memory Slave: SA8

#### STD 32 Compliance

Permanent Master: Classes supported-{Requirements} Options Temporary Master: Classes supported-{Requirements} Options I/O Slave: Classes supported-{Requirements} Options Memory Slave: Classes supported-{Requirements} Options Arbiter (Mn, Dn): Classes supported-{Requirements} Options

Figure 8. STD 32 compliance format